摘要: 通過視頻接口和Channel Link芯片實現(xiàn)了數(shù)字信號處理芯片TMS320DM642與Camera Link線掃描相機的無縫連接。解決了圖像數(shù)據(jù)輸出速度為40 MB/s的高速圖像數(shù)據(jù)采集系統(tǒng)中,前端采集與后端輸出的速度匹配問題。系統(tǒng)可實時、高速地采集大量的圖像數(shù)據(jù)。

圖像采集的運用非常廣泛,經過幾十年的發(fā)展,采集技術有了很大程度的進步。目前的專業(yè)采集設備集成度更高,分辨率更大,傳輸速度更快,針對性更強。

本文以DALSA公司的Spyder2系列線掃描相機為圖像采集源,以TI公司的TMS320DM642多媒體處理器為核心,實現(xiàn)高速圖像的采集和處理任務。

Spyder2線掃描相機以其高速的采集速度和先進的Camera Link接口,已廣泛應用于工業(yè)生產線等領域。本方案集合了Camera Link和TMS320DM642的優(yōu)點,縮短了設計周期,降低了難度,提高了設計的效率和設計質量。

1 總體概述

Camera Link 是一種基于視頻應用發(fā)展而來的通信接口標準,Camera Link接口采用National Semiconductor公司的Channel Link技術,其最高速率可達2.38Gbps。Camera Link相機和圖像采集設備之間采用LVDS信號傳輸,從而簡化了圖像采集設備和模擬攝像頭之間所必需的視頻編解碼等步驟,降低了生產成本和維護費用。

TMS320DM642作為多媒體處理器,內置3個專用的視頻數(shù)據(jù)接口(Video Port)。每一視頻接口有20位數(shù)據(jù)總線,可以在8位、10位、16位總線方式下進行視頻采集或視頻顯示。采集頻率最高可達80MHz。

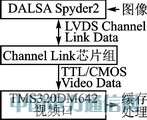

DALSA Spyder2相機采用單通道Channel Link輸出,每線輸出2048像素,每個像素8位。為了圖像處理的方便,采集接口將視頻數(shù)據(jù)重整為完整幀并緩存于SDRAM中。TMS320DM642的Video Port接口設置為8位的RAW Data采集模式。總體結構如圖1所示。DALSA Spyder2相機采集到的視頻信號通過Video Port 0傳輸?shù)絊DRAM中緩存,DM642再通過EMIFA從SDRAM中讀取每幀圖像進行分析處理。

圖1 總體結構圖

2 關鍵硬件設計

2.1 視頻解串電路

Camera Link標準中,相機的信號被分為3種:視頻數(shù)據(jù)信號、相機控制信號、串行通信信號。

視頻解碼部分采用National Semiconducor公司TSSOP56封裝的DS90CR288A接收器來完成,它能夠將4路LVDS串行數(shù)據(jù)流轉換為2位并行TTL/CMOS數(shù)據(jù),在傳輸時鐘CLK的每個周期,將28位并行數(shù)據(jù)輸出。

DS90CR288A解碼出的TTL/CMOS信號可以分成2類:圖像信號和圖像時鐘信號(WCLK)。其中圖像信號又由24位圖像數(shù)據(jù)信號和4位圖像同步信號組成,這些信號都符合Channel Link技術標準。

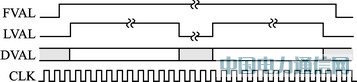

圖像同步信號包括:FVAL(Frame Valid)、LVAL(Line Valid)、DVAL(Data Valid),分別為幀有效信號、行有效信號和數(shù)據(jù)有效信號。當FVAL、LVAL、DVAL同時有效(為高電平時),表示相機正在輸出有效的圖像數(shù)據(jù)。Channel Link的圖像同步信號和時鐘信號的關系如圖2所示。

圖2 視頻同步信號時序圖

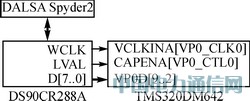

DALSA Spyder2 相機為線掃描數(shù)字攝像機,設置為8位灰度輸出,相機在每個時鐘的上升沿傳送串行圖像信號,F(xiàn)VAL、DVAL信號廠商固定為高電平,只由LVAL信號控制相機的圖像輸出。針對這一特性,設計充分利用TMS320DM642的視頻接口這一優(yōu)勢,由圖像時鐘(WCLK)來控制視頻口的采集時鐘(VP0_CLK0),相機的行有效信號(LVAL)控制視頻口的采集使能端(VP0_CTL0),圖像信號D[7..0]送往Video Port的數(shù)據(jù)總線VP0D[9..2]。采集接口與TMS320DM642的視頻口連接原理圖如圖3所示。

圖3 Camera與TMS320DM642接口示意圖

當相機輸出一行有效圖像數(shù)據(jù)時,TMS320DM642的視頻口在圖像時鐘的上升沿將解串的圖像信號采集到視頻口的內部高速FIFO中。當內部FIFO緩存超過編程門限(threshold)后將自動觸發(fā)一個專用EMDA通道將FIFO中的圖像數(shù)據(jù)搬移到SDRAM中。整個視頻的采集過程都沒有DSP干預,避免了由于數(shù)據(jù)搬運而引發(fā)的錯誤同時減少了數(shù)據(jù)傳輸?shù)南到y(tǒng)資源開銷。

2.2 相機控制電路

Camera Link標準中規(guī)定了4位相機控制信號:CC1、CC2、CC3和CC4,需要一個4位的LVDS驅動器,DALSA Spyder2 相機遵循Camera Link標準采用了CC1、CC2、CC3三個相機控制位,分別完成外部同步控制、像素重置控制和采集方向控制,CC4控制位暫時閑置。采用National Semiconducor公司的DS90LV047A芯片來驅動這4位相機控制信號,如圖4所示。

圖4 相機控制電路示意圖

DS90LV047A將CPLD發(fā)送過來的外部控制信號轉化為符合LVDS標準的控制信號。相機控制信號的使用是可選擇的,像DALSA Spyder2系列,沒有控制信號的參與也能完成采集。

2.3 相機通信電路

DALSA Spyder2相機需要一組由9600bps、一個開始位、一個結束位、無校驗位組成的串行異步信號(±SerTFG、±SerTC)來進行相機參數(shù)的設置和信息反饋。本設計選用了National Semiconducor公司的DS90LV019集成驅動器/接收器來進行TTL/LVDS轉換,如圖5所示。

圖5 相機通信電路示意圖

DS90LV019有4種工作模式,模式的選擇由DE和/RE兩個信號的狀態(tài)決定。當DE和/RE都為高時,IC工作在驅動模式;當DE和/RE都為低時,IC工作于接收模式;當DE為低,/RE為高時,IC工作在三態(tài)模式;當DE為高,/RE為低時,IC工作在全雙工模式。這里采用一片DS90LV019作為串行通信LVDS信號的收發(fā)器,工作于全雙工模式。再用Maxim公司的MAX3221來進行TTL/RS232電平間的轉換。控制端通過RS232接口發(fā)送的相機命令再通過DS90LV019傳送給相機,相機接收后給出的反饋信息再通過DS90LV019和MAX3221傳送給控制端。

3 軟件設計

DDK是TI公司用來簡化設備驅動程序開發(fā)的軟件套件,它提供了一些外設的完全驅動函數(shù),其中就有Video Port專用的Minidriver驅動程序庫。

視頻驅動程序主要包括微驅動、類驅動和中間接口3個方面的設計。視頻采集驅動程序中,在GIO類驅動程序的基礎上進一步封裝成FVID類。將微驅動細分為視頻端口類和制定的編解碼芯片微驅動,兩者之間通過外部設備控制接口EDC實現(xiàn)對外圍芯片的打開、控制和關閉等操作。

為了實現(xiàn)Camera Link相機圖像數(shù)據(jù)的采集,TMS320DM642的視頻口必須被配置為RAW DATA采集方式。與通常的BT.656采集方式不同,當Video Port工作于RAW DATA采集方式下,TMS320DM642不會進行數(shù)據(jù)選擇和數(shù)據(jù)判斷,而BT.656方式需要判斷SAV/EAV同步碼,RAW DATA采集方式主要用于從ADC獲取原始的圖像數(shù)據(jù)。

在RAW DATA采集方式下,當CAPEN信號(VP0_CTL0)被使能時,Video Port開始采集VP0D數(shù)據(jù)線上的數(shù)據(jù),采樣數(shù)據(jù)的大小可以通過VCxSTOP1的VCXSTOP和VCYSTOP位進行設置,通過VCXSTOP和VCYSTOP的組合,TMS320DM642允許單幀最多采集4096Kb個采樣數(shù)據(jù)。當采集數(shù)據(jù)達到VCXSTOP和VCYSTOP所設置的值的時候,采樣完成,此后,CAPEN信號必須保持至少2個時鐘周期的無效狀態(tài)。系統(tǒng)中設置采集幀大小為2048pix×256pix,及采集524288個數(shù)據(jù)后打包為一幀,系統(tǒng)采用相機的時鐘WCLK=25ns,行有效周期LVAL=50μs,行無效周期為150μs,150μs>>25ns,能保證CAPEN至少2個時鐘周期無效狀態(tài)的要求。

幀同步處理對于RAW DATA方式的圖像采集是一個很關鍵的因素。由于RAW DATA采集方式的數(shù)據(jù)不包含任何類似于BT.656數(shù)據(jù)流那樣的幀啟/停標識碼(SAV/EAV CODE),也不提供外部的水平和垂直同步信號,幀同步時無法實現(xiàn)的,所以DDK自帶的Minidriver驅動程序無法完成RAW DATA方式的圖像采集,則需要對Minidriver驅動進行修改來實現(xiàn)RAW DATA采集,通過設置Video Port的第一場采樣開始寄存器VCxSTRT1,并增加采樣垂直消隱間隔VCVBLNKP和開始同步使能位SSE來間接的實現(xiàn)幀同步功能。修改后的視頻采集結構為:

typedef struct {

Int cmode;//采集模式選擇

Int fldOp;//場/幀操作

/*8~15位*/

Int scale;//1/2縮放使能

Int resmpl;//灰度采集使能

Int bpk10Bit;//10位采集模式

/*16~23位*/

Int hCtRst;//水平計數(shù)復位模式

Int vCtRst;//垂直計數(shù)復位模式

Int fldDect;

Int extCtl;//使能外部時鐘控制

Int fldInv;//使能場反轉

/*原始模式采集參數(shù)*/

Uint16 sse;//開始同步使能位

Uint16 vcvblnkp;//垂直消隱間隔

Uint16 sse; //開始同步使能位

Uint16 vcvblnkp; //垂直消隱間隔

Uint16 fldXStrt1; //場1 X開始

Uint16 fldYStrt1; //場1 Y開始

Uint16 fldXStrt2; //場2 X開始

Uint16 fldYStrt2; //場2 Y開始

Uint16 fldXStop1; //場1 X停止

Uint16 fldYStop1; //場1 Y停止

Uint16 fldXStop2; //場2 X停止

Uint16 fldYStop2; //場2 Y停止

Uint16 thrld;//視頻FIFO閾值

/*幀緩存設定*/

Int numFrmBufs; //緩存幀數(shù)

Int alignment;//幀緩存對齊方式

Int segId;//存儲分配ID

/*EDMA優(yōu)先等級*/

Int edmaPri;//EDMA通道優(yōu)先級

Int irqId;

} VPORTCAP_Params;

當SSE位被置位且視頻口采樣使能信號有效,在2個垂直消隱間隔以后,視頻口開始采集數(shù)據(jù)。通過設置VCVBLNKP位,可以定義一個垂直消隱信號時間的長度。為了保證能在一幀數(shù)據(jù)開始的時候同步,系統(tǒng)將VCVBLNKP置位為0。

此外,系統(tǒng)采用的是DS90CR288A相機解碼芯片,不同于DDK中使用的SAA7121解碼芯片,所以在相機的接口配置中(VPORT_PortParams)需要對EDC接口進行修改。

DS90CR288A主要包括打開和關閉兩個操作,可以通過對外部CPLD中的相機控制寄存器VIDEO_CLR置位來操作。修改得到的EDC控制函數(shù)如下:

static EDC_Handle Camera_open(String devName, Arg optArg){

Int devId;

if(devName[0] != '/') {

devId = -1;//無效端口

} else if(devName[1] == '0') {

devId = 0;

VIDEO_CLR = 0x1;//0號端口,寄存器置高,使能解碼

} else if(devName[1] == '1'){

devId = 1;

VIDEO_CLR = 0x1;//1號端口,寄存器置高,使能解碼

} else {

devId = -1;//無效端口

}

return (EDC_Handle)devId;

}

static Int Camera_close(EDC_Handle handle){

VIDEO_CLR = 0x0;//寄存器置低,停止解碼

return EDC_SUCCESS;

}

4 結論

本設計實現(xiàn)了TMS320DM642通過Video Port與Camera Link相機的無縫連接,硬件接口設計簡單,系統(tǒng)編程也很方便。整個圖像的采集都不用CPU的參與,可以提高整個系統(tǒng)的工作效率。

參考文獻

[1] 曾義芳. DSP開發(fā)應用技術[M].北京航空航天大學出版社,2008.

[2] 胡越黎,王俊,曹家麟.基于TMS320C6711的圖像處理系統(tǒng)設計[D].上海:上海大學, 2005.

[3] 劉瓊,安濤,金剛. DM642+CPLD視頻采集處理系統(tǒng)設計[J]. 儀器儀表用戶,2007(3).

[4] 湯金寬,曹丹華,吳裕斌.用DSP技術從模擬視頻信號中獲取數(shù)字圖像[J].單片機與嵌入式系統(tǒng)應用,2005(8).

[5] 胡嘉凱,蔣建國,齊美彬.基于TMS320DM642的編程[J].電子產品世界, 2006(4).

[6] 彭程.基于TMS320C64x/DM64x的視頻編碼優(yōu)化[OL].[201012].http://www.pcbfans.cn/article/e9/8263$3.html.

[7] 趙建偉,尹崗.基于DM642的數(shù)字圖像采集小系統(tǒng)[D].呼和浩特:內蒙古工業(yè)大學, 2006.

[8] Texas Instruments.TMS320DM642 Video/Imaging FixedPoint Digital Signal Processor (SPRS200L),2007.

[9] Texas Instruments.TMS320C6000 DSP External Memory Interface(EMIF) Reference Guide(SPRU266A), 2003.

[10] Texas Instruments.Interfacing a CMOS Sensor to the TMS320DM642 Using Raw Capture Mode(SPRAA52), 2004.