š¬ę¬Ż║×ķ┴╦┐sČ╠ŠĒĘeŠÄ┤aŲ„įOėŗų▄Ų┌Ż¼╩╣ė▓╝■įOėŗĖ³Š▀ņ`╗ŅąįŻ¼į┌ĮķĮBŠĒĘeŠÄ┤aŲ„įŁ└ĒĄ─╗∙ĄA╔ŽŻ¼šō╩÷┴╦ę╗ĘN╗∙ė┌┐╔ŠÄ│╠▀ē▌ŗŲ„╝■Ż¼▓╔ė├─ŻēK╗»įOėŗĘĮĘ©Ż¼└¹ė├VHDLė▓╝■├Ķ╩÷šZčįīŹ¼F(xi©żn)CDMA2000ŽĄĮy(t©»ng)Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─ĘĮĘ©Ż¼Įo│÷┴╦į┌Quartusó“▄ø╝■Ž┬Ą─Ę┬šµĮY╣¹Ż¼▓óį┌FPGAŲ„╝■╔Ž“×ūCīŹ¼F(xi©żn)ĪŻĘ┬šµ║═īŹ“×Č╝ūC├„┴╦▀@ĘNĘĮĘ©Ą─┐╔ąąąį║═š²┤_ąįĪŻ

0 ę²čį

į┌═©ą┼ŽĄĮy(t©»ng)ųąŻ¼ė╔ė┌öĄ(sh©┤)ūųą┼╠¢į┌é„▌ö▀^│╠ųą╩▄ĄĮĖ„ĘNĖ╔ö_Ą─ė░ĒæŻ¼╩╣ą┼╠¢┤aį¬▓©ą╬ūāē─Ż¼╣╩é„▌ö?sh©┤)ĮĮė╩šČ╦║¾┐╔─▄░l(f©Ī)╔·Õeš`┼ąøQŻ¼×ķĮŌøQ▀@ę╗å¢Ņ}Ż¼═©│Żį┌įOėŗöĄ(sh©┤)ūų═©ą┼ŽĄĮy(t©»ng)ĢrŻ¼╩ūŽ╚æ¬Å─║Ž└ĒĄž▀xō±š{(di©żo)ųŲųŲČ╚ĪóĮŌš{(di©żo)ĘĮĘ©ęį╝░░l(f©Ī)╦═╣”┬╩Ą╚ĘĮ├µ┐╝æ]Ż¼╚¶▓╔╚Īęį╔Ž┤ļ╩®╚įļyØMūŃę¬Ū¾Ż¼Š═ę¬┐╝æ]▓ŅÕe┐žųŲ┤ļ╩®ĪŻį┌CDMA 2000ŽĄĮy(t©»ng)Ą─Ū░Ž“µ£┬Ę║═Ę┤Ž“µ£┬ĘųąŠ═▓╔ė├┴╦ŠĒĘeŠÄ┤aüĒīŹ¼F(xi©żn)Ū░Ž“▓ŅÕe┐žųŲ(FEC)ĪŻ

FPGA╩Ū┐╔ŠÄ│╠▀ē▌ŗŲ„╝■Ż¼╦³Ą─ų„ę¬ā×(y©Łu)³cį┌ė┌┐╔ęįĮĶų·EDA╣żŠ▀═©▀^▄ø╝■ŠÄ│╠ī”Ų„╝■Ą─ė▓╝■ĮYśŗ║═╣żū„ĘĮ╩Į▀MąąųžśŗŻ¼▀@Š═╩╣Ą├ė▓╝■įOėŗŠ▀ėą▄ø╝■įOėŗĄ─ņ`╗Ņąį║═▒ŃĮ▌ąįĪŻ▒ŠįOėŗ▓╔ė├VHDLšZčį▓ó▀xė├┐╔ŠÄ│╠▀ē▌ŗŲ„╝■į┌Quartusó“Ž┬üĒīŹ¼F(xi©żn)CDMA 2000ŽĄĮy(t©»ng)ųąĄ─Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„ĪŻ

1 ŠĒĘeŠÄ┤aŲ„įŁ└Ē

ŠĒĘe┤a╩Ūė╔P.Eliasį┌1954─Ļ╩ūŽ╚╠ß│÷üĒĄ─Ż¼╦³╩Ūę╗ĘNĘŪĘųĮM┤aŻ¼═©│Ż╦³Ė³▀mė├ė┌Ū░Ž“╝mÕeŻ¼ę“×ķŲõąį─▄ī”ė┌įSČÓīŹļHŪķør│Żā×(y©Łu)ė┌ĘųĮM┤aŻ¼Č°ŪęįOéõ║åå╬ĪŻūįÅ─A.J.Viterbiė┌1967─Ļ░l(f©Ī)¼F(xi©żn)┴╦ę╗ĘNėąą¦Ą─ūg┤a╦ŃĘ©Ż¼▓óė╔J.Omuraė┌1969─ĻūC├„▀@╩Ūę╗ĘNMLūg┤a╦ŃĘ©║¾Ż¼╩╣ė├Vit-erbiūg┤a╦ŃĘ©Ą─ŠĒĘe┤aŠ═│╔×ķ¼F(xi©żn)┤·═©ą┼ŽĄĮy(t©»ng)ųą▒ž▓╗┐╔╔┘Ą─ŠÄ┤aĘĮ░ĖĪŻCDMA 2000ŽĄĮy(t©»ng)ęÓ▓╔ė├┤╦ĘNŠÄ┤aĘĮ░ĖĪŻ

1.1 ŠĒĘeŠÄ┤aŲ„įŁ└Ē

┼cĘųĮM┤aŠÄ┤aŲ„▓╗═¼Ż¼ŠĒĘe┤aŠÄ┤aŲ„╩ŪėąėøæøĄ─Ż¼╝┤Ż║ŠÄ┤aŲ„į┌╚╬║╬ę╗Č╬Ģrķgā╚(n©©i)«a(ch©Żn)╔·Ą─néĆ┤aį¬Ż¼▓╗āH╚ĪøQė┌▀@Č╬ĢrķgųąĄ─kéĆą┼Žó╬╗Ż¼Č°Ūę▀Ć╚ĪøQė┌Ū░N-1Č╬ęÄ(gu©®)Č©Ģrķgā╚(n©©i)Ą─ą┼Žó╬╗Ż╗╝┤ŠÄ┤aŲ„«a(ch©Żn)╔·Ą─néĆ┤aį¬Ė·š²į┌ęŲ╚ļĄ─├┐ę╗éĆk╬╗Ą─ą┼Žó▒╚╠žėąĻPĪŻ×ķ┴╦▒Ńė┌šf├„å¢Ņ}Ż¼į┌▀@└’ęÄ(gu©®)Č©Ż║ŠÄ┤a┬╩r=k/nĪŻŲõųąŻ¼k▒Ē╩Šę╗┤╬ęŲ╚ļŠÄ┤aŲ„Ą─ą┼Žó╬╗öĄ(sh©┤)Ż╗n▒Ē╩Šī”æ¬ė┌ęŲ╚ļk╬╗ą┼ŽóŠÄ┤aŲ„▌ö│÷Ę¹╠¢öĄ(sh©┤)ĪŻ┤╦═ŌŻ¼ė├K▒Ē╩Š╝s╩°ķLČ╚Ż¼╦³Ą╚ė┌ŠÄ┤aŲ„ųąęŲ╬╗╝─┤µŲ„Ą─╝ēöĄ(sh©┤)Ż╗īŹļH╔ŽŻ¼Ą┌ę╗éĆęŲ╬╗╝─┤µŲ„╩ŪČÓėÓĄ─ĪŻ

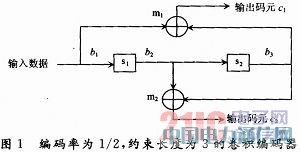

├Ķ╩÷ŠĒĘeŠÄ┤a▀^│╠Ą─ĘĮĘ©║▄ČÓŻ¼╚ńŻ║ČÓĒŚ╩ĮĘ©ĪóŠžĻćĘ©ĪóśõĀŅłD║═ŠW(w©Żng)Ė±łDĄ╚ĪŻ▀@└’▓╔ė├┼cŠĒĘeŠÄ┤aŲ„ĮYśŗ├▄ŪąŽÓĻPĄ─ČÓĒŚ╩ĮĘ©üĒšf├„ŠĒĘe┤aĄ─ŠÄ┤aįŁ└ĒĪŻęčų¬ę╗éĆŠÄ┤a┬╩r=1/2Ż¼╝s╩°ķLČ╚K=3Ą─ŠĒĘeŠÄ┤aŲ„Ż¼ŲõŠĒĘe┤aĄ─╔·│╔ČÓĒŚ╩ĮŠžĻć×ķŻ║

╩ĮųąŻ║D×ķčė▀t╦ŃūėŻ¼╔·│╔ČÓĒŚ╩ĮĄ─Ą┌ę╗ĒŚ×ķ1+D2Ż¼▒Ē╩ŠŠÄ┤aŲ„▌ö│÷Ą─Ą┌ę╗éĆ┤aį¬c1Ą╚ė┌▌ö╚ļ┤aį¬b1┼cŪ░▌ö╚ļ┤aį¬b3Ą──Ż2║═Ż╗ŲõĄ┌Č■ĒŚ×ķD+D2Ż¼▒Ē╩Š▌ö│÷Ą─Ą┌Č■éĆ┤aį¬c2×ķŪ░ā╔éĆ▌ö╚ļ┤aį¬b2║═b3Ą──Ż2║═ĪŻ

Ė∙ō■(j©┤)ŠĒĘe┤aĄ─╔·│╔ČÓĒŚ╩ĮŠžĻć┐╔ų▒ĮėĄ├ĄĮŠÄ┤aŲ„Ą─ĮYśŗłDŻ¼╚ńłD1╦∙╩ŠĪŻłDųąs1Ż¼s2×ķęŲ╬╗╝─┤µŲ„Ż╗m1Ż¼m2×ķ─Ż2║═╝ėĘ©Ų„Ż╗Ųõųąb1┤·▒Ē«öŪ░▌ö╚ļĄ─ą┼Žó╬╗Ż╗ęŲ╬╗╝─┤µŲ„ĀŅæB(t©żi)b2Ż¼b3┤µā”ęįŪ░Ą─ą┼Žó╬╗Ż╗c1Ż¼c2┤·▒ĒŠÄ┤a║¾Ą─▌ö│÷┤aį¬ĪŻ

į┌ŠĒĘe┤aĄ─ŠÄ┤a▀^│╠ųąŻ¼ŠÄ┤aŲ„Å─╚½┴ŃĀŅæB(t©żi)│÷░l(f©Ī)Ż¼ūŅ║¾▒žĒÜ╗žĄĮ╚½┴ŃĀŅæB(t©żi)Ż¼╣╩«ö╦══Ļą┼Žó║¾Ż¼▀Ćꬎ“ŠÄ┤aŲ„į┘╦═╚ļK-1Č╬╚½┴Ńą┼ŽóŻ¼ęįŲ╚╩╣ŠÄ┤aŲ„╗žĄĮ╚½┴ŃĀŅæB(t©żi)ĪŻįO┤╦ŠÄ┤aŲ„Ą─Ų╩╝ĀŅæB(t©żi)×ķ┴ŃŻ¼╝┤b1b2b3×ķ000ĪŻ«ö▌ö╚ļĄ─ą┼Žó╬╗×ķ11010ĢrŻ¼×ķ▒ŻūC▌ö╚ļĄ─╚½▓┐ą┼Žó╬╗Č╝─▄═©▀^ęŲ╬╗╝─┤µŲ„Ż¼▓óī”ęŲ╬╗╝─┤µŲ„▀MąąÅ═╬╗Ż¼▒žĒÜį┌ą┼Žó╬╗║¾╝ė╝s╩°ķLČ╚£pę╗éĆ┴ŃŻ¼╝┤ā╔éĆ┴ŃŻ╗┤╦Ģrī”æ¬Ą─▌ö│÷┤aį¬ą“┴ą×ķŻ║10111001011100Ż¼üGŚē║¾╦─╬╗┐╔Ą├ŠÄ┤aŲ„Ą─▌ö│÷ą┼ŽóŻ║1011100101ĪŻš¹éĆ╣żū„▀^│╠ųąŠÄ┤aŲ„Ą─ĀŅæB(t©żi)╚ń▒Ē1╦∙╩ŠĪŻ

1.2 CDMA 2000ŽĄĮy(t©»ng)ųąĄ─Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„

į┌CDMA 2000ŽĄĮy(t©»ng)ųąŻ¼Ū░Ž“µ£┬Ę╩╣ė├ŠÄ┤a┬╩×ķ1/2Ż¼╝s╩°ķLČ╚×ķ9Ą─ŠĒĘeŠÄ┤aŲ„ĪŻŪ░Ž“µ£┬ĘŠĒĘe┤aĄ─╔·│╔ČÓĒŚ╩ĮŠžĻć×ķŻ║

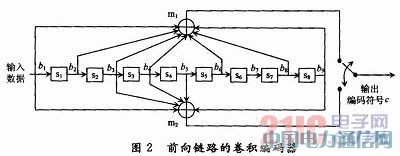

ė╔┤╦╔·│╔ČÓĒŚ╩ĮŠžĻć┐╔Ą├Ū░Ž“ŠÄ┤aŲ„Ą─ĮYśŗłDŻ¼╚ńłD2╦∙╩ŠĪŻłDųąs1Ī½s8×ķęŲ╬╗╝─┤µŲ„Ż╗m1Ż¼m2×ķ─Ż2║═╝ėĘ©Ų„Ż╗Ųõųąb1┤·▒Ē«öŪ░▌ö╚ļĄ─ą┼Žó╬╗Ż╗ęŲ╬╗╝─┤µŲ„ĀŅæB(t©żi)b2Ī½b9┤µā”ęįŪ░Ą─ą┼Žó╬╗Ż╗c┤·▒ĒŠÄ┤a║¾Ą─▌ö│÷┤aį¬ĪŻ

2 CDMA 2000ŽĄĮy(t©»ng)ųąŪ░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─īŹ¼F(xi©żn)

2.1 CDMA 2000Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─ļŖ┬ĘĮM│╔

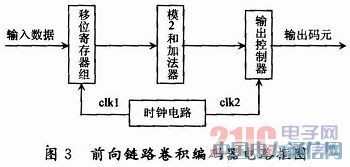

įōįOėŗ▓╔ė├─ŻēK╗»Ą─įOėŗĘĮĘ©Ż¼Ė∙ō■(j©┤)CDMA2000ŽĄĮy(t©»ng)ųąĄ─Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─╣”─▄īóŲõā╚(n©©i)▓┐ĮYśŗĘų×ķŻ║ęŲ╬╗╝─┤µŲ„ĮMĪó─Ż2║═╝ėĘ©Ų„Īó▌ö│÷┐žųŲŲ„ęį╝░ĢrńŖļŖ┬ĘĄ╚╦─éĆ─ŻēKŻ¼├┐ę╗─ŻēKī”æ¬ę╗▓┐ĘųVHDLĄ─įOėŗ╬─╝■Ż¼▀@śė└¹ė┌│╠ą“Ą─ŠÄīæ║═š{(di©żo)įćŻ¼Å─Č°ĮĄĄ═┴╦š¹éĆ│╠ą“Ą─š{(di©żo)įćļyČ╚Ż¼╠ßĖ▀┴╦▄ø╝■Ą─┐╔ŠSūoąį║═┐╔ūxąįĪŻŪ░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─ĮM│╔┐“łD╚ńłD3╦∙╩ŠĪŻ

ŲõųąŻ¼ĢrńŖą┼╠¢clk1║═clk2┐╔ė╔╗∙šŠ┐žųŲŲ„(BSC)Ą─ĢrńŖļŖ┬Ęų▒Įė╠ß╣®Ż¼╗“ė╔▒Š┤╬įOėŗĄ─ĢrńŖļŖ┬Ęīó╗∙šŠ┐žųŲŲ„(BSC)╠ß╣®Ą─įŁ╩╝ĢrńŖą┼╠¢▀MąąĘųŅlĄ├ĄĮŻ╗▌ö│÷┐žųŲŲ„░³└©▌ö│÷öĄ(sh©┤)ō■(j©┤)║Ž│╔ļŖ┬Ę║═š¹ą╬ļŖ┬Ęā╔▓┐ĘųĪŻ

2.2 CDMA 2000Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─Ę┬šµīŹ¼F(xi©żn)

Ė∙ō■(j©┤)ŠĒĘeŠÄ┤aŲ„ļŖ┬Ę┐“łDŻ¼▓╔ė├VHDLšZčįŠÄīæŪ░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─į┤│╠ą“▌ö╚ļĄĮQuartusó“ķ_░l(f©Ī)▄ø╝■ųą▀MąąŠÄūgĪóĘ┬šµĪóŠC║ŽĄ├ĄĮ┐╔Ž┬▌d╬─╝■Ż¼╚╗║¾═©▀^ī”Ų„╝■ŠÄ│╠═Ļ│╔įOėŗĪŻ

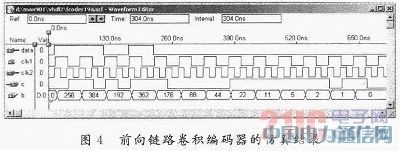

Ę┬šµŪ░╝┘įOŠÄ┤aŲ„Ą─│§╩╝ĀŅæB(t©żi)×ķ┴ŃŻ¼╝┤Ż║b1Ī½b9×ķ00000000Ż╗▌ö╚ļĄ─ą┼Žó×ķ11010Ż¼×ķ▒ŻūC▌ö╚ļĄ─╚½▓┐ą┼Žó╬╗Č╝─▄═©▀^ęŲ╬╗╝─┤µŲ„Ż¼▓óī”ęŲ╬╗╝─┤µŲ„▀MąąÅ═╬╗Ż¼į┌ą┼Žó╬╗║¾╝ė8éĆ┴ŃŻ¼Ųõ▌ö│÷ĮY╣¹×ķ11010111000001111111101100,Ż¼Ę┬šµĢrŻ¼▌ö╚ļöĄ(sh©┤)ō■(j©┤)dataĄ─╦┘┬╩×ķ9.6Kb/sŻ╗▌ö│÷┤aį¬cĄ─╦┘┬╩×ķ19.2Kb/sĪŻĘ┬šµĮY╣¹╚ńłD4╦∙╩ŠŻ¼Ųõųąb×ķ╝─┤µŲ„ĮMĖ„éĆĢr┐╠Ą─ĀŅæB(t©żi)ĪŻ

į┌Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ą─įOėŗųąėąę╗ą®ąĶę¬ūóęŌĄ─å¢Ņ}Ż║╩ūŽ╚ę¬├„┤_VHDLšZčį▓╗═¼ė┌Ųõ╦¹Ą─ėŗ╦ŃÖCšZčįŻ¼╦³╩Ūę╗ĘNė▓╝■├Ķ╩÷šZčįŻ¼╦³├Ķ╩÷Ą─ī”Ž¾╩Ū┐═ė^Ą─ļŖ┬ĘŽĄĮy(t©»ng)ĪŻŲõ┤╬Ż¼▓╗═¼Ą─EDA╣żŠ▀ī”VHDLšZčįĄ─ų¦│ų│╠Č╚▓╗═¼ĪŻ▒Š┤╬įOėŗųą▓╔ė├Ą─Quartusó“ķ_░l(f©Ī)╣żŠ▀ų„ę¬╩Ūßśī”┐╔ŠÄ│╠▀ē▌ŗŲ„╝■Ą─▄ø╝■Ż¼╦³▓ó▓╗ų¦│ų╦∙ėąĄ─VHDLšZŠõŻ¼╦³ų╗ų¦│ųRTL╝ē├Ķ╩÷Ż¼▓╗ų¦│ųąą×ķ╝ē├Ķ╩÷ĪŻį┘ėąŻ¼į┌įOėŗųąąĶę¬Ė∙ō■(j©┤)įOėŗę¬Ū¾║═┐╔ŠÄ│╠▀ē▌ŗŲ„╝■Ą─┘Yį┤ŪķørĪó╦┘Č╚Ą╚▀Mąą║Ž└ĒĄ─▀xō±ĪŻįōįOėŗųą▓╔ė├Ą─EP2C8Q208Ų„╝■Š═┐╔ØMūŃ┘Yį┤║═╦┘Č╚ĘĮ├µĄ─ę¬Ū¾ĪŻ

3 ĮYšZ

▒Š╬─īŹ¼F(xi©żn)┴╦ę╗ĘN▀mė├ė┌CDMA 2000ŽĄĮy(t©»ng)Ą─Ū░Ž“µ£┬ĘŠĒĘeŠÄ┤aŲ„Ż¼═©▀^ī”š¹¾wļŖ┬ĘĄ─įOėŗĪóĘ┬šµ║═š{(di©żo)£yŻ¼ĮY╣¹▒Ē├„▒ŠŠÄ┤aŲ„┐╔▀_ĄĮCDMA 2000ŽĄĮy(t©»ng)ę¬Ū¾Ż¼Š▀ėąę╗Č©Ą─īŹė├ārųĄŻ¼═¼ĢrŻ¼▒ŠįOėŗ▓╔ė├╗∙ė┌┐╔ŠÄ│╠▀ē▌ŗŲ„╝■ĮĶų·VHDLšZčį╝░EDA╣żŠ▀▀MąąįOėŗĄ─╦╝┬ĘŻ¼┤¾┤¾┐sČ╠┴╦įOėŗų▄Ų┌Ż¼ĮĄĄ═┴╦│╔▒ŠŻ¼╠ßĖ▀┴╦įOėŗĄ─┐╔┐┐ąįĪóņ`╗ŅąįŻ¼×ķ═©ą┼ŽĄĮy(t©»ng)įOėŗ╠ß╣®┴╦ę╗ĘNėąą¦Ą─įOėŗĘĮĘ©ĪŻ